この記事での学習内容 基本情報 応用情報

プロセッサを構成する制御装置と演算装置の役割,それらを構成する加算器,レジスタ,デコーダ(命令解読器,復号器)などの役割,プロセッサの能力とシステムの処理能力の関係を理解する。また,命令実行時のレジスタの動作を理解する。

用語例:アキュムレータ,補数器,乗算器,積和演算器,命令アドレスレジスタ(命令カウンタ, プログラムカウンタ, 逐次制御カウンタ), IR ( Instruction register:命令レジスタ),GR(General Register:汎用レジスタ),インデックスレジスタ( 指標レジスタ), ベースレジスタ, MAR ( Memory Address Register:メモリアドレスレジスタ),DR(Data Register:データレジスタ),MR(Memory Register:メモリレジスタ),スタックポインタ

制御装置と演算装置の役割

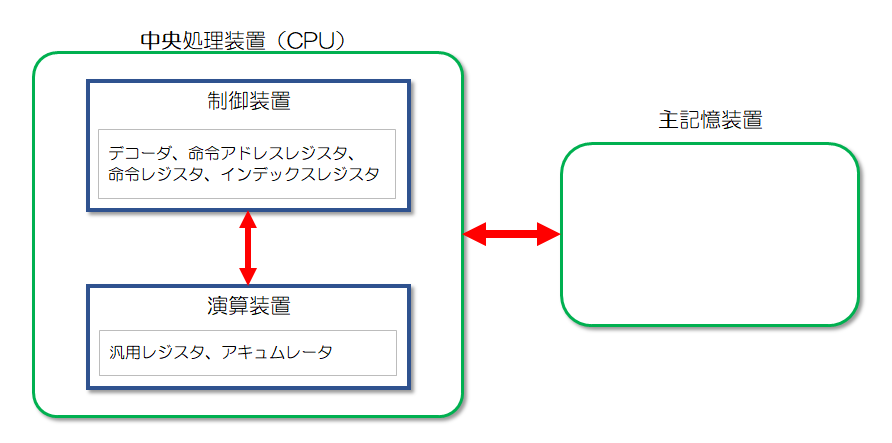

コンピュータの五大機能のうち、中核となる制御と演算は、高速な中央処理装置(CPU)で行われます。LSIチップであるCPUの内部は、制御装置と演算装置とで構成されています。

演算装置は、それぞれの命令を実行する電子回路の集まりです。

制御装置は、コンピュータ全体の処理の進行を制御する電子回路です。

レジスタ

レジスタとは、CPUの内部に存在する高速の記憶装置です。計算入力や計算結果の一時的な保持や、周辺機器の動作状態の保持に利用されます。

大容量で相対的に低速な記憶装置の中のデータは、CPUの中の高速なレジスタへ移して処理します。

これによって処理を高速にしつつ、装置間の回路を単純にします。レジスタの動作は非常に高速ですが、容量は少量です。

レジスタは複数存在し、いくつかの種類があります。代表的なレジスタは以下の表のとおりです。

| 名称 | 役割 |

|---|---|

| アキュムレータ | 演算結果を一時的に格納するレジスタ |

| 命令アドレスレジスタ | 次に実行する命令の先頭アドレスを格納するレジスタ |

| 命令レジスタ | 現在実行中の命令を格納するレジスタ |

| 汎用レジスタ | 様々な目的で利用することが出来るレジスタ |

| インデックスレジスタ (指標レジスタ) | インデックスアドレス指定で、基準となるアドレスを格納するレジスタ |

| ベースレジスタ | ベースアドレス指定で、基準となるアドレスを格納するレジスタ |

命令アドレスレジスタ

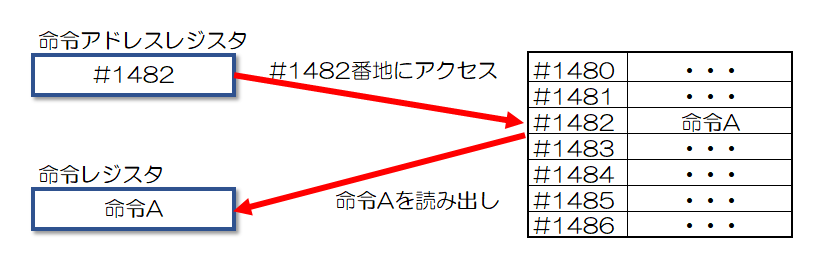

命令アドレスレジスタは、制御装置の中にあるレジスタの一種であり、次に実行する記憶装置中の命令の先頭アドレスを格納するレジスタです。命令カウンタやプログラムカウンタとも呼ばれます。

通常は、一つの命令の演算が終わると、命令アドレスレジスタには次の命令の先頭アドレスが格納されます。これによって、複数の命令が並んだ順序に実行されます。

一方、プログラム言語の反復、選択、サブルーチンの呼び出しや再帰に対応する分岐命令は、分岐先の命令の先頭先アドレスを命令アドレスレジスタに格納する働きをします。

命令レジスタ

命令レジスタは、現在実行中の命令を格納するレジスタです。命令アドレスレジスタが指す記憶装置の中の命令が次々と格納されていきます。

汎用レジスタ

汎用レジスタは、演算やアドレス保持などの様々な用途を持つレジスタです。どんな用途で使うかは命令で指示します。

汎用レジスタは、電子回路を簡潔にし、プログラミングの自由度を増します。インデックスレジスタやベースレジスタを用途に含む場合もあります。

インデックスレジスタ

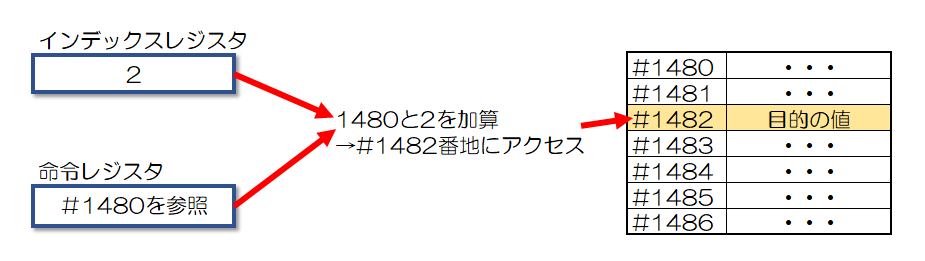

インデックスレジスタは、アドレスを扱うレジスタの一種です。指標レジスタともいいます。

命令に含まれるアドレス値に、レジスタに格納されているインデック値を加算する機能を持っています。

そのインデックス値は、プログラム言語の配列のインデックス値(添字)に相当するので、配列処理のプログラムが簡潔になります。

ベースレジスタ

ベースレジスタは、アドレスを扱うレジスタの一種です。命令に含まれるアドレス値に、レジスタに格納されているベース値を加算する機能を持っているのが特徴です。仕組みとしては、インデックスレジスタと変わりはなく、用途と呼称が違うだけです。

ベースレジスタの値を変えるだけで、プログラムの主記憶装置中の位置を自由に再配置したり、命令のアドレス用ビット数を節約したりする役割を果たします。

インデックスレジスタとベースレジスタの使い分け

簡単に両者の違いを言い表すならば、実行時にリロケータブルにするために、ベースアドレス方式を使い、配列要素を参照するためにインデックスアドレス方式を使う、というのが一般的な使い分け方です。

デコーダの役割

デコーダは、符号や暗号、圧縮状態に変えられていたデータを、元のデータに変換するハードウェアやソフトウェアです。

CPUの制御装置の中にある命令デコーダは、記憶装置から命令レジスタに移された命令コードを解釈して、命令の実行の準備をして、命令コードに対応する電子回路を選択する電子回路です。例えば、命令コードが「加算」を意味しているなら、演算装置の加算回路が実行されるようにします。

(参考)プログラムの再利用性に関するキーワード

再配置可能(リロケータブル)

プログラムを補助記憶装置から主記憶装置に読み込む際、主記憶のどの位置に読み込んでも実行が可能なプログラムを再配置可能なプログラムといいます。アドレス指定が、プログラムの先頭アドレスからの相対位置で表現されている必要があります。

再使用可能(リユーザブル)

主記憶に読み込まれて実行を終えたプログラムが、再度の主記憶への読み込みを行うことなく再実行できることをいいます。

再帰可能(リカーシブル)

自分自身を呼び出すことが可能なものを再帰可能なプログラムといいます。

再入可能(リエントラント)

1つのプログラムにおいて、複数の処理要求が来ても同時に処理できることを指します。各データが処理中に混合しないように、データの領域を処理要求の数だけ用意しています。