この記事での学習内容 基本情報 応用情報

・AND 回路,OR 回路,NOT 回路などの基本となる論理回路の組合せによって半加算器,全加算器が実現され,演算が行われていることを理解する。

・代表的な機械語命令の種類,命令語の構成,命令の実行手順(命令の取出し,命令部の解読,データの取出し,命令の実行),アドレス修飾を理解する。また,機械語演算のバイナリ表現,アセンブラの記号表現との対応,相互の変換を行う方法を理解する。

・割込みの仕組み,内部割込み,外部割込みに分類される割込みの種類,多重割込み時の処理を理解する。

用語例:順序回路,組合せ回路,NAND 回路、算術演算命令,論理演算命令,転送命令,比較命令,分岐命令,シフト命令,入出力命令,アドレス部(オペランド),フェッチ,アドレス計算,アドレス方式,アドレス修飾,直接アドレス指定,間接アドレス指定,インデックスアドレス指定(インデックス修飾),ベースアドレス指定,相対アドレス指定,絶対アドレス指定,即値アドレス指定,有効アドレス(実効アドレス)、SVC(SuperVisor Call)割込み,入出力割込み,割込み制御,マシンチェック割込み,プログラム割込み

加算機

加算器は、CPUの中にある2進数を加算する電子回路です。デジタル回路によって計算装置を発明する時に、考察の中心となった電子回路です。

加算器は、最下位の桁用の一つの半加算器と、それ以上の桁用の複数の全加算器とで構成されます。

半加算器

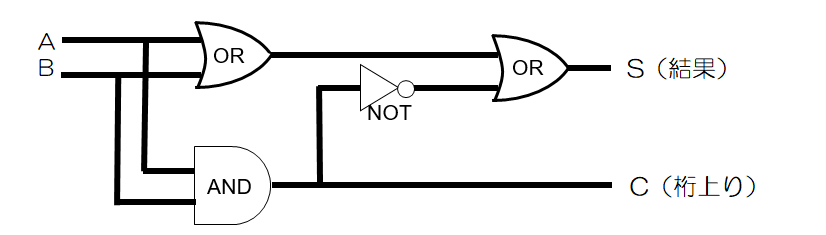

2進数の加算の一部を担う半加算器という電子回路は、AND・OR・NOTの3種類の論理回路の組み合わせで実現できます。

桁上りの信号は2桁目の全加算器へ送ります。

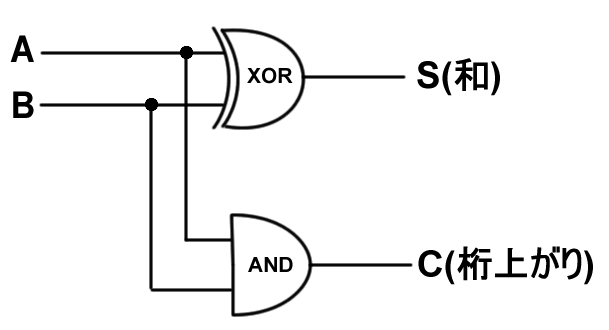

なお、半加算器を実現するには、上図の例以外にも色々な電子回路の組み合わせが考えられますが、排他的論理和(XOR)回路が使えるのであれば、下記のようにXORとANDの組合せが最も簡単です。

全加算器

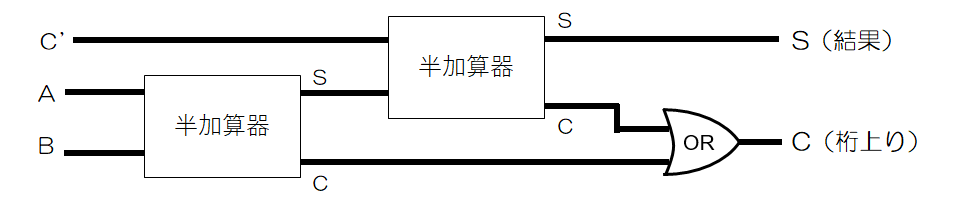

2進数の加算の一部を担う全加算器という電子回路は、2つの半加算器と1つのOR回路で実現できます。

下位の桁用の回路から桁上りの信号を受け取り、それ自身の桁上りの信号は上位桁用の全加算器へ送ります。

命令とアドレス指定

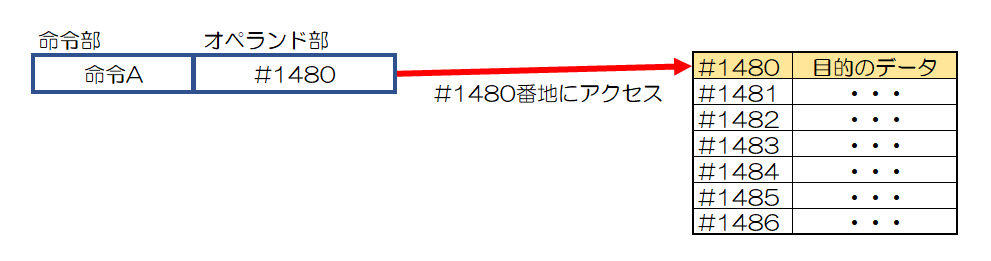

一つの命令の形式は、CPUの種類や命令の種類によって異なりますが、典型的な命令の形式は「命令部」と「オペランド部」で構成されます。

命令部は命令の種類を表し、オペランド部は処理する対象のアドレス(主記憶装置中の位置)を表します。

命令の実行手順

一つの命令の実行は、一般には次のような細かい段階を経て進められます。細部は命令の種類によって異なる場合もあります。

- 命令の読み込み:

次に実行するべき一つの命令を、主記憶装置からCPUの命令レジスタへ読み込む。 - 命令の解読:

命令の命令部を解読して、以降の処理の種類を選ぶ。 - アドレスの決定:

命令のオペランド部を解読して、処理スべき主記憶装置中の位置を決定する。 - データの読み込み:

主記憶装置からデータをレジスタに読み込む。 - 命令の実行:

選んだ演算処理の回路が演算などの処理をする。 - データの書き出し:

レジスタからデータを主記憶装置に書き出す。

アドレス指定

直接アドレス方式

命令のオペランド部の値には、処理対象のアドレスが直接示されています。

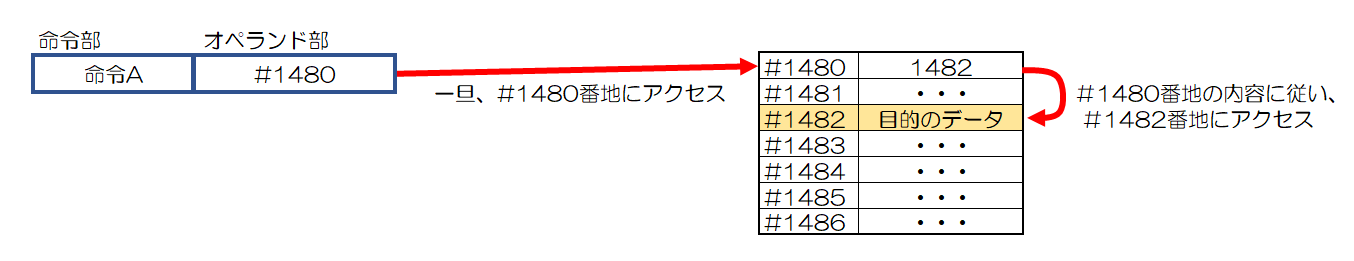

間接アドレス指定方式

間接アドレス指定方式は、命令のオペランド部が指す「主記憶装置中の値」を最終的なアドレスとする方式です。

プログラムの実行中に主記憶装置中の値を変更することによって、最終的なアドレスを変更できます。

インデックスアドレス指定方式

インデックスアドレス指定方式は、オペランド部の値にインデックスレジスタの値を加えてアドレスを決定する方式です。

プログラム言語の配列の処理に役立ちます。

ベースアドレス指定方式

ベースアドレス指定方式は、オペランド部の値にベースレジスタの値を加えてアドレスを決定する方式です。プログラムを再配置自由にしたり、アドレスを表すオペランド部のビット数を節約したりするのに役立ちます。

相対アドレス指定方式

相対アドレス指定方式は、オペランド部の相対アドレス地に命令アドレスレジスタのアドレス値を加えてアドレスを決定する方式です。プログラムを主記憶装置中の任意の位置に再配置するのに適しています。

インデックスアドレス指定方式、ベースアドレス指定方式、および相対アドレス指定方式の仕組みは同じであり、用途や呼称が異なるだけです。

割込みの仕組み

割込みは、一つのプログラムの一連の命令の実行を中断することです。割込みによって別のプログラムの一連の命令を実行した後、中断していたプログラムの実行を再開します。

複数のプログラム全体の処理効率を向上させたり、例外状態に対処したりするのに役立ちます。

割込み発生時には、CPU内のレジスタ類の内容は他の記憶場所(スタック領域)へ退避して、再開する時に元通りにします。

割込みには、実行中のプログラムが原因で行われる内部割込みと、実行中のプログラム以外が原因で行われる外部割込みとがあります。

内部割込み

内部割込みは、実行中のプログラムが原因で行われる割込みです。内部割込みには次のようなものがあります。

- 演算結果が許容範囲を越えようとする例外状態の割込み

- 決定したアドレスが許容範囲を越えようとする例外状態の割込み。

- プログラムが意図的に起こす割込み。(入出力装置用のプログラムに処理を依頼する時にスーパーバイザコールという命令を実行するときなど)

SVC割込み

スーパーバイザコール(SVC)割込みは、プログラム中のスーパーバイザコール命令を実行して発生させる割込みです。

入出力装置用のプログラムに処理を依頼するときなど、プログラム自身が意図的に割込みをしたい場合に用いられます。

外部割込み

外部割込みは、実行中のプログラム以外が原因で行われる割込みです。外部割込みには次のようなものがあります。

- 入出力処理が完了したり、入出力処理で異常が発生したりした場合の割込み。

- そのプログラムへ割当てた単位時間が終了した時のタイマ割込。

入出力割込み

入出力割込みは、入出力処理が完了したり、入出力処理で以上が発生したりした場合に発生する割込みです。

CPUの処理は入出力装置の処理に比べてケタ違いに高速なので、CPUが単純に入出力装置の処理の完了の終了を待つのは非常に効率が悪くなります。そのため、該当のプログラムが入出力処理の完了を待っている間に、CPUは他のプログラムを並行して処理します。入出力割込みによって、元のプログラムの実行を再開します。

タイマ割込み

タイマ割込みは、そのプログラムへ割当てた単位時間が終了した時に発生する割込です。

正確なタイミングを必要とする処理や、複数のプログラムに平等に時間を割り当てて処理する場合などに用いられます。